### 高性能多模式PWM控制芯片

### 概述

AP8268是一款高集成度的电流模式PWM控制芯片,具有高性能、低待机功耗、低成本等特点。AP8268通过QR-PWM、QR-PFM、Burst-mode的三种模式混合调制技术,实现了低待机功耗和全电压范围下的最佳效率,频率调制技术和SoftDriver技术充分保证良好的EMI表现。AP8268同时提供了全面的管脚开短路保护,以及逐周期过流保护、VDD过压保护、欠压锁存、过温保护、输出过压保护、过载保护、输出二极管短路保护等功能。

### 产品特征

- 軟启动功能

- QR-PWM、QR-PFM、Burst-mode混合模式提高效率 (AP8268A带QR功能, AP8268B不带QR功能)

- 专利的频率抖动技术提高EMI性能

- 内部集成斜率补偿功能

- 高低压分频功能

- 自适应的线电压补偿功能

- 全面的保护功能包括

- ◆ 过温保护 (OTP)

- ◆ 输出过压保护

- ◆ 逐周期过流保护 (OCP)

- ◆ 输出开/短路保护

- ◆ 专利的DMG电阻开/短路保护(Latch模式)

- ◇ 次级整流管短路保护

- ◆ 过载保护(OLP)

### 应用领域

- 待机电源

- 开放式开关电源

- 适配器

### 封装/订购信息

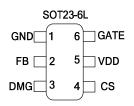

| 订购代码          | 封装       | 版本差异   |

|---------------|----------|--------|

| AP8268ATCC-R1 | SOT23-6L | 带QR功能  |

| AP8268BTCC-R1 | SOT23-6L | 不带QR功能 |

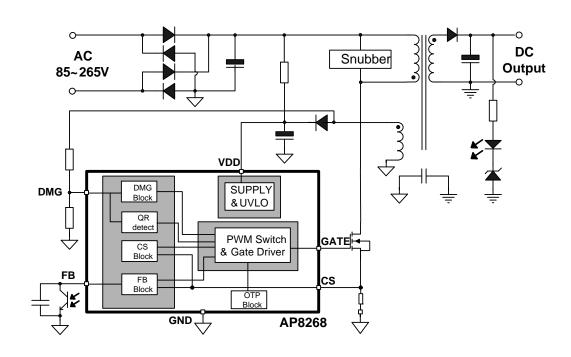

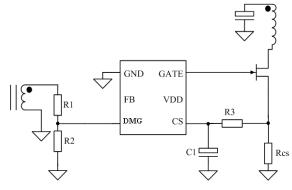

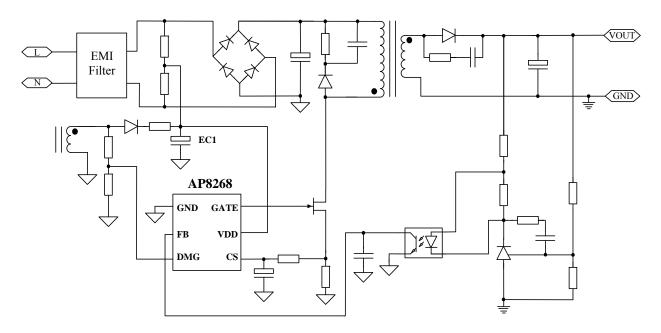

## 典型应用

## 管脚定义

| 管脚名  | 管脚标号 | 管脚功能描述                    |

|------|------|---------------------------|

| GND  | 1    | 地                         |

| FB   | 2    | 反馈输入引脚, FB脚与CS脚共同控制PWM占空比 |

| DMG  | 3    | 去磁引脚, 通过电阻分压采样输出电压和输入电压   |

| CS   | 4    | 电流检测输入引脚                  |

| VDD  | 5    | 芯片供电引脚                    |

| GATE | 6    | 图腾柱输出,用于驱动MOSFET          |

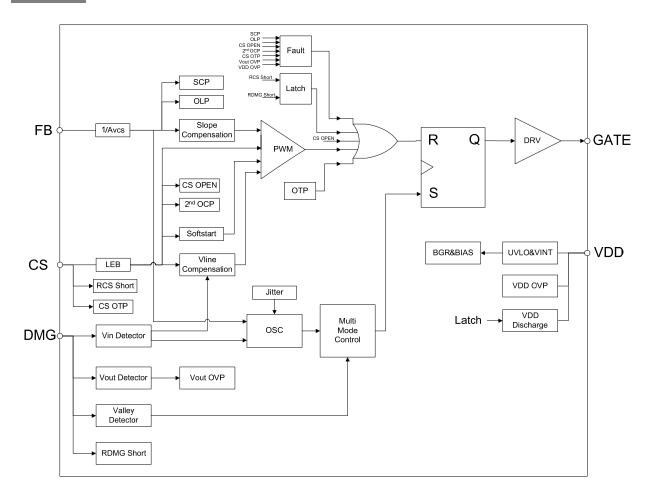

## 功能框图

## 极限工作范围

| VDD 脚耐压0.3~45V                      | 管脚焊接温度 (10秒)260℃                       |

|-------------------------------------|----------------------------------------|

| FB, CS, DMG 脚耐压0.3~7V               | 封装热阻 Rθ <sub>JA</sub> (SOT23-6L)260℃/W |

| GATE 脚耐压0.3~15V                     | 人体模式 ESD 能力 <sup>(1)</sup> (HBM) 4kV   |

| 存储温度范围55~150℃                       | 机器模式 ESD 能力 <sup>(1)</sup> (MM)        |

| A 字 1 字目毛标体二子亚拉拉四世世纪PGD上述(PGD / /PF |                                        |

备注: 1. 产品委托第三方严格按照芯片级ESD标准(ESDA/JEDEC JDS-001-2014)中的测试方式和流程进行测试。

## 电气特性

(T<sub>A</sub> = 25°C, V<sub>DD</sub>=15V, 除非另有说明)

| 参数                    | 符号                     | 条件               | 最小值      | 典型值  | 最大值  | 单位  |

|-----------------------|------------------------|------------------|----------|------|------|-----|

| VDD电压部分               |                        |                  |          |      |      |     |

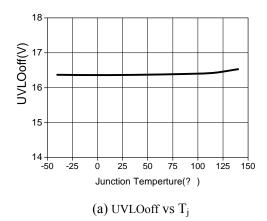

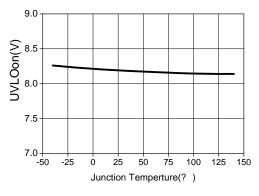

| VDD启动阈值电压             | UVLOoff                |                  | 15.5     | 16.5 | 17.5 | V   |

| VDD欠压保护阈值电压           | UVLOon                 |                  | 7        | 8    | 9    | V   |

| VDD过压保护电压             | OVP                    |                  | 38       | 40.5 | 43   | V   |

| 上拉 PMOS 开启时 VDD<br>电压 | Vpull-up               |                  |          | 10   |      | V   |

| VDD锁存电压               | Vlatch                 |                  |          | 5    |      | V   |

| VDD电流部分               |                        |                  | <u>.</u> |      |      |     |

| 启动态电流                 | $I_{VDD\_ST}$          | VDD=UVLOoff-1V   |          | 2    | 10   | uA  |

| 开关态工作电流               | $I_{\mathrm{VDD0}}$    | VFB=3.5V,CS=0.3V |          | 2.5  | 3    | mA  |

| 间歇态工作电流               | $I_{VDD1}$             | VFB=0.5V,CS=0.3V |          | 0.55 | 1.5  | mA  |

| 保护态工作电流               | I <sub>VDD_Fault</sub> | FB floating      |          | 0.4  | 1    | mA  |

| 震荡器部分                 |                        |                  |          |      |      |     |

| 开关频率                  | Г                      | IDMG>330uA       | 60       | 65   | 70   | kHz |

| 开关频率 Fosc             |                        | IDMG<330uA       |          | 90   |      | kHz |

| 间歇态工作频率               | Fosc_BM                |                  | 22       | 25   | 28   | kHz |

| 频抖调制频率                | F_jitter               |                  |          | 30   |      | Hz  |

| 频抖范围                  | $\triangle Fosc$       |                  |          | ±6   |      | %   |

| FB检测部分                |                        |                  |          |      |      |     |

| FB 开路电压               | $V_{FB}$               |                  |          | 5.1  |      | V   |

| FB 短路电流               | $I_{FB\_SHORT}$        |                  |          | 0.2  |      | mA  |

| 最大占空比                 | Dmax                   |                  | 70       | 80   | 90   | %   |

| 进入降频模式阈值电压            | $ m V_{FB\_PFM\_L}$    | IDMG>330uA       |          | 2.45 |      | V   |

|                       |                        | IDMG<330uA       |          | 1.85 |      | V   |

| 退出降频模式阈值电压            | $V_{{ m FB\_PFM\_H}}$  | IDMG>330uA       |          | 2.7  |      | V   |

| <b>必山阵</b>            |                        | IDMG<330uA       |          | 2    |      | V   |

| 进入间歇模式阈值电压            | $V_{FB\_BM\_L}$        |                  |          | 1.15 |      | V   |

| 退出间歇模式阈值电压            | $V_{FB\_BM\_H}$        |                  |          | 1.25 |      | V   |

# **AP8268**

| 参数               | 符号           | 条件                   | 最小值 | 典型值  | 最大值 | 单位     |

|------------------|--------------|----------------------|-----|------|-----|--------|

| 过载保护阈值电压         | Vth_OLP      |                      | 4.1 | 4.4  | 4.7 | V      |

| 过载保护延迟时间         | Td_OLP       |                      |     | 60   |     | ms     |

| CS电流检测部分         |              |                      |     |      |     |        |

| 软启动时间            | Tss          |                      |     | 6    |     | ms     |

| 前沿消隐时间           | TLEB         |                      |     | 400  |     | ns     |

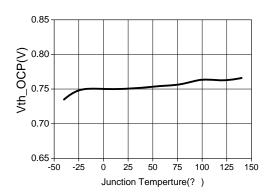

| 过流保护阈值           | Vth_OCP      |                      | 0.7 | 0.75 | 0.8 | V      |

| 次级整流短路保护阈值<br>电压 | $ m V_{DSP}$ |                      |     | 1.1  |     | V      |

| 次级整流短路保护         | T.I. DCD     |                      |     | 7    |     | 1      |

| 延迟时间             | Td_DSP       |                      |     | 7    |     | cycles |

| DMG检测部分          |              |                      |     |      |     |        |

| 过压保护阈值电压         | Vth_DOVP     |                      | 2.7 | 3    | 3.3 | V      |

| DMG 过压保护延迟时间     | Td_DOVP      |                      |     | 7    |     | cycles |

| 最大时钟开启等待时间       | Thold        |                      |     | 5    |     | us     |

| 斜坡补偿最小占空比        | Duty_Slope   | Fosc=65kHz           |     | 35   |     | %      |

| 最大开启时间           | Ton_max      |                      |     | 12   |     | us     |

| GATE 驱动部分        |              |                      |     |      |     |        |

| 输出低电平            | VOL          |                      |     |      | 1   | V      |

| 输出高电平            | VOH          |                      | 6   |      |     | V      |

| 输出钳位电压           | V_clamping   | CS=0.3V,FB=3V        |     | 12   |     | V      |

| 输出上升时间           | T_r          | 1.2V~10.8V@CL=1000pF |     | 60   |     | ns     |

| 输出下降时间           | T_f          | 10.8V~1.2V@CL=1000pF |     | 20   |     | ns     |

| 过温保护部分           | •            |                      | •   |      | •   |        |

| 过温保护温度           | $T_{SD}$     |                      |     | 150  |     | °C     |

| 过温保护回差           | $T_{HYST}$   |                      |     | 30   |     | °C     |

www.chipown.com

## 特性曲线

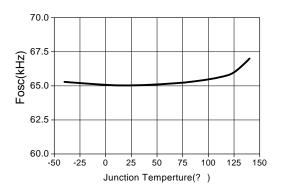

(c) F<sub>OSC</sub> vs T<sub>j</sub>

(b) UVLOon vs T<sub>j</sub>

(d) Vth\_OCP vs T<sub>j</sub>

### 功能描述

#### 1. 启动

AP8268的启动电流相当低,故VDD电压可快 速的被充电到大于UVLO阈值电压UVLOoff,因此 可使用一个较大的启动电阻用于减小损耗,同时 获得较快的启动速度。当VDD电压达到16.5V,芯 片开始工作。启动过程结束后,变压器辅助绕组 对Vpp电容提供能量。

#### 2. 软启动

启动阶段,CS脚内部的最大峰值电流电压限 制逐步的提高;可以大大减小器件的应力,防止变 压器饱和。软启动时间典型值为6ms。

#### 3. 振荡器

AP8268 在 PWM 模式振荡频率固定, 当 I<sub>DMG</sub>>330uA时,系统处于高输入电压段,此时工作 频率为65kHz,当IDMG<330uA时,系统处于低输入 电压段,此时工作频率为90kHz。AP8268通过提高 低输入压时的工作频率,可降低对变压器的要求。 根据DMG上偏电阻设置线电压分频点。

#### 4. 降频工作模式

AP8268提供降频工作模式,通过检测FB脚电 压,在轻载和空载条件下降低开关频率以提高轻载 效率。当FB脚电压小于V<sub>FB PFM L</sub>,芯片进入降频工 作模式, 开关频率随负载降低而降低, 直至最小频 率25kHz。

#### 5. 谷底开通 (AP8268A)

AP8268根据开关管波形计算励磁电感与寄生 电容振荡周期,在DCM模式下实现精确谷底开通, 提高转换效率。

#### 6. 间歇工作模式

极轻载时,AP8268进入间隙工作模式以减小 待机功耗。当负载减轻,反馈电压减小;当FB脚 电压小于V<sub>FB BM L</sub> (典型1.15V),芯片进入间歇工 作模式,功率管关断。当FB脚超过V<sub>FB BM H</sub>时,开 关管再次导通。

#### 7. 输出驱动

AP8268的输出级采用的是图腾柱结构,用于 驱动外部MOSFET的栅极。死区时间防止了电源 到地的直接通路, 既降低了功耗, 同时又保证了 高压驱动管不被烧坏。输出驱动的最大电压被内 部的齐纳二极管箝位在12V。AP8268经过优化的 输出驱动电路, 可减小开关损耗同时又有很好的 EMI特性。

#### 8. 斜坡补偿

AP8268采用峰值电流控制,内置斜坡补偿功 能,通过将电压锯齿信号叠加在采样电压信号上, 以改善系统闭环稳定性。

#### 9. 自适应的线电压补偿

AP8268通过DMG引脚上偏电阻检测输入电压, 从而产生线补偿电流Ic到CS引脚,其中  $I_{LC}$ =K\* $I_{DMG}$ ,K=0.375为采样DMG引脚电流的比例 系数。线补偿电流I<sub>LC</sub>通过偏置连接在CS引脚与CS 检测电阻Rcs间的电阻R3产生补偿电压,补偿量的 大小由电阻R3的阻值决定。

2018年3月

#### 10. 过压保护

AP8268通过在消磁阶段采样辅助绕组电压, 实现精确的过压保护。当采样的DMG平台电压大于3V且持续7个PWM周期, 触发输出OVP保护, 输出关闭。通过选择合适的DMG下偏电阻R2阻值来设置DMG OVP保护点。

#### 11. 过载保护

负载电流超过预设定值时,系统会进入过载保护;在异常情况下,可对系统进行保护。当 $V_{FB}$ 电压超过4.4V,经过固定60ms的延迟时间,开关模式停止。

#### 12. 过温保护

AP8268集成了片上过温保护,当芯片温度超过150℃,芯片进入过温保护状态。

## 典型应用电路

### 外围参数选择参考

为了更好体现 AP8268 的性能,请务必遵守以下规则:

1. VDD 电容 EC1 应放置在距离 VDD 引脚和 GND 引脚最近的地方。

Rev.1803 2018年3月

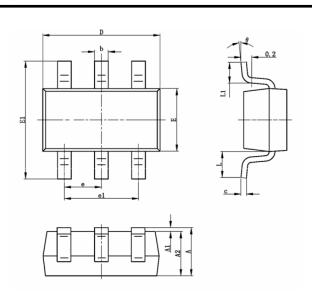

## <u>封装信息</u>

### SOT23-6L 封装外形及尺寸

| 尺寸 符号 | 最小(mm) | 最大(mm) | 尺寸<br>符号 | 最小(mm)   | 最大(mm) |

|-------|--------|--------|----------|----------|--------|

| A     | 1.050  | 1.250  | E1       | 2.650    | 2.950  |

| A1    | 0.000  | 0.100  | e        | 0.950TYP |        |

| A2    | 1.050  | 1.150  | e1       | 1.800    | 2.000  |

| b     | 0.300  | 0.400  | L        | 0.700REF |        |

| С     | 0.100  | 0.200  | L1       | 0.300    | 0.600  |

| D     | 2.820  | 3.020  | Θ        | 8°TYP    |        |

| Е     | 1.500  | 1.700  |          |          |        |

| 型号      | 表层丝印  | 封装       |

|---------|-------|----------|

| AP8268A | 69XXX | SOT22 (I |

| AP8268B | 68XXX | SOT23-6L |

备注: XXX 为内部代码

#### 备注:

- 1. 此制图可以不经通知进行调整;

- 2. 器件本体尺寸不含模具飞边;

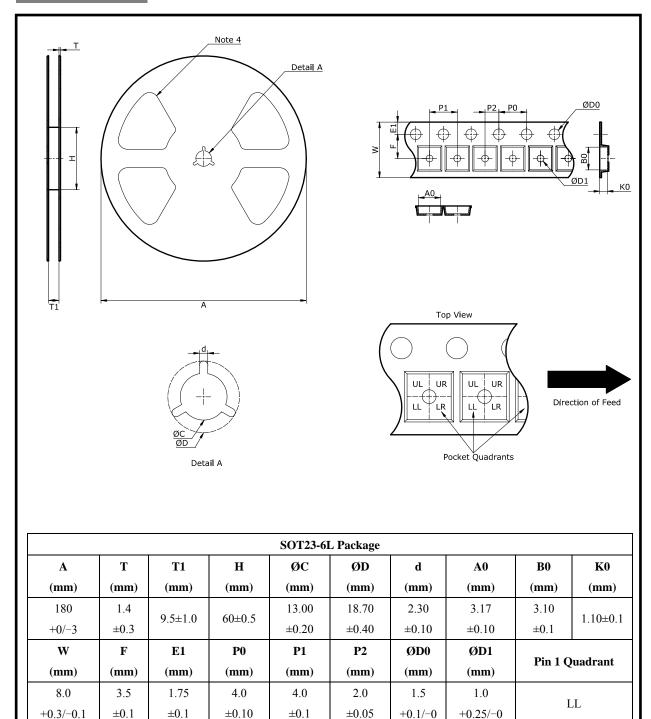

## 编带及卷轴信息

#### 备注:

- 1. 此制图可以不经通知进行调整;

- 2. 所有尺寸是毫米公制的标称值;

- 3. 此制图并非按严格比例,且仅供参考。客户可联系芯朋销售代表获得更多细节;

- 4. 此处举例仅供参考。

Rev.1803

2018年3月

## 重要声明

无锡芯朋微电子股份有限公司保留更改规格的权利, 恕不另行通知。无锡芯朋微电子股份有限公司对任何将其产品用于特殊目的的行为不承担任何责任, 无锡芯朋微电子股份有限公司没有为用于特定目的产品提供使用和应用支持的义务。无锡芯朋微电子股份有限公司不会转让其专利许可以及任何其他的相关许可权利。

www.chipown.com